摘 要

集成电路(IC)的核心是芯片。每块集成电路芯片在使用前都需要封装。封装是IC芯片支撑、保护的必要条件,也是其功能实现的主要组成部分。随着芯片及集成的水平不断提高,电子封装的作用正变得越来越重要。当今芯片封装技术发展也越来越快,以满足不断快速增长的电子产品的需求。文章介绍了几种芯片封装技术的特点,并对未来的发展趋势及方向进行了初步分析。从中可以看出IC芯片与微电子封装技术相互促进,协调发展密不可分的关系。

1 什么是封装

关注电脑核心配件发展的朋友都会注意到,厂商通常在推出革命性的CPU、内存或者芯片组时,都会强调产品采用了新的封装形式。不过,很多人对封装并不了解。那么究竟什么是封装?它对电脑硬件的发展有什么意义?

封装技术其实就是一种将集成电路打包的技术。拿我们常见的内存来说,我们实际看到的体积和外观并不是真正的内存的大小和面貌,而是内存芯片经过打包即封装后的产品。这种打包对于芯片来说是必须的,也是至关重要的。因为芯片必须与外界隔离,以防止空气中的杂质对芯片电路的腐蚀而造成电气性能下降。另一方面,封装后的芯片也更便于安装和运输。由于封装技术的好坏还直接影响到芯片自身性能的发挥和与之连接的PCB(Print Circuit Board,印刷电路板)的设计和制造,因此它是至关重要的。封装也可以说是指安装半导体集成电路芯片用的外壳,它不仅起着安放、固定、密封、保护芯片和增强导热性能的作用,而且还是沟通芯片内部世界与外部电路的桥梁—芯片上的接点用导线连接到封装外壳的引脚上,这些引脚又通过印刷电路板上的导线与其他器件建立连接。因此,对于很多集成电路产品而言,封装技术都是非常关键的一环。芯片的封装技术种类实在是多种多样,诸如DIP、QFP、TSOP、BGA、CSP等等,一系列名称看上去都十分繁杂,其实,只要弄清芯片封装发展的历程也就不难理解了。芯片的封装技术已经历经好几代的变迁,技术指标一代比一代先进,包括芯片面积与封装面积之比越来越接近,适用频率越来越高,耐温性能越来越好,以及引脚数增多,引脚间距减小,重量减小,可靠性提高,使用更加方便等等,都是看得见的变化,而促使这种变化的最根本因素来自于市场需求。从80年代中后期开始,电子产品正朝着便携式/小型化、网络化和多媒体化方向发展,这种市场需求对电路组装技术提出了相应的要求:单位体积信息的提高(高密度化);单位时间处理速度的提高(高速化)。为了满足这些要求,势必要提高电路组装的功能密度,这就成为了促进芯片封装技术发展的最重要的因素。CPU和其他超大型集成电路在不断发展,集成电路的封装形式也不断作出相应的调整变化,而封装形式的进步又将反过来促进芯片技术向前发展。

2 开山鼻祖——DIP

DIP(Dual In-line Package)封装又被称为双列直插式封装,它应该是人们最为熟悉的封装技术之一。早在4004、8086和8088等CPU中便得到了应用,如图1。DIP有一个厚厚的外壳,从其两侧伸出两列向下弯曲的外部引脚。DIP封装的最大优点就是适合在PCB板上实现穿孔焊接,操作起来比较简单,因此在现有半导体业中,DIP仍然占有一席之地,诸如某些BIOS芯片上就能见到它的身影。当然,DIP的缺点还是相当明显的,芯片封装面积和厚度都相对较大,由此也造成了整个芯片体积的增大。与此同时,外部引脚容易在芯片的插拔过程当中损坏,不太适用于高可靠性场合。此外,DIP封装还有一个致命的缺陷,那就是它只适用于引脚数目小于100 的中小规模集成电路,对于发展迅猛的芯片领域来说,100引脚的限制是“致命”的,也正是这个原因,DIP慢慢退出了CPU封装的舞台。

3 早期强豪——QFP

当CPU发展到80286时代,封装技术的鼻祖DIP已经不适合其需求了,QFP(Plastic Quad Flat Package,塑料方形扁平式封装)出现了。与DIP相比,QFP同样采用了引脚方式,不同的是改变了引脚从两列伸出的方式,而是芯片四面全部有引脚,并且引脚从直插式改为了欧翘状,如图2,引脚间距可以更密,引脚可以更细。如此一来,在整个芯片面积不变的情况下可以容纳更多的引脚,同时信号稳定性好,能够满足芯片高频率工作的需求。正是因为这些优点,使得QFP封装在80286时代得到了广泛采用,并成为了当时高密度封装的唯一选择。

为了适应电路组装密度的进一步提高,QFP的引脚间距目前已从1.27 mm发展到了0.3 mm。由于引脚间距不断缩小, I/O 数不断增加,封装体积也不断加大,给电路组装生产带来了许多困难,导致成品率下降和组装成本的提高。另方面由于受器件引脚框架加工精度等制造技术的限制,0.3 mm已是QFP引脚间距的极限,这都限制了组装密度的提高。0.5 mm引脚间距、304条引脚已经是目前电子封装生产所能制造QFP封装的最大值,若要容纳更多的引脚,只有寻找更新的封装,种种迹象表明QFP封装已经走到了发展的尽头。

4 一代强手——TSOP封装技术

20世纪80年代,内存第二代的封装技术TSOP(图3)出现了,并得到了业界的广泛认可。时至今日TSOP仍旧是内存封装的主流技术。TSOP是“ThinSmall Outline Package”的缩写,中文意思是薄型小尺寸封装。TSOP封装是在芯片的周围做出引脚,采用SMT技术(表面贴装技术)直接附着在PCB板的表面。TSOP封装适合高频应用环境,可靠性也比较高。同时TSOP封装具有成品率高、价格便宜等优点,得到了极为广泛的应用。

TSOP封装方式中,内存芯片是通过芯片引脚焊接在PCB板上的,焊点和PCB板的接触面积较小,使得芯片向PCB板传热就相对困难。而且TSOP封装方式的内存在频率超过150 MHz后,会产生较大的信号干扰和电磁干扰。由于这样的特点,使得TSOP封装在SDRAM、DDR SDRAM时代大放异彩,不少知名内存制造商如三星、现代、Kingston等目前都在采用这项技术进行内存封装。但到了DDR2时代由于内存需要更高的频率,所以TSOP才被BGA/CSP等封装逐步替代。

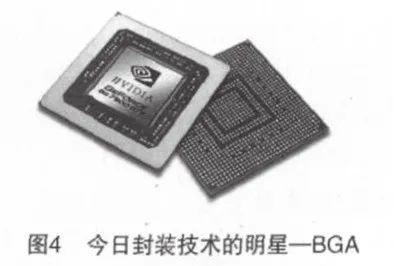

5 中流砥柱——BGA/CSP

20世纪90年代随着集成技术的进步、设备的改进和深亚微米技术的使用,芯片集成度不断提高,I/O 引脚数急剧增加,功耗也随之增大,对集成电路封装的要求也更加严格。为满足发展的需要,在原有封装方式的基础上,又增添了新的方式-球栅阵列封装,简称BGA(Ball Grid Array Package)。BGA封装技术已经在GPU(图形处理芯片)、主板芯片组等大规模集成电路的封装领域得到了广泛的应用。它的 I/O 引线以圆形或柱状焊点按阵列形式分布在封装下面,引线间距大,引线长度短,这样BGA消除了精细间距器件中由于引线而引起的共面度和翘曲的问题。BGA技术的优点是可增加I/O数和间距,消除QFP技术的高引脚数带来的生产成本和可靠性问题。如图4所示的NVIDIA公司的GeForce图形芯片(GPU)体现了当前工程技术的最高成就,相信看到芯片照片上那1144个焊球的人都会惊叹不已。BGA一出现便成为CPU、图形芯片、主板上南/北桥芯片等高密度、高性能、多引脚封装的最佳选择。

概括起来,和QFP相比,BGA的优点主要有以下几点:

(1) I/O 引线间距大(如1.0 mm,1.27 mm),可容纳的 I/O 数目大(如1.27 mm间距的BGA在25 mm边长的面积上可容纳350个 I/O ,而0.5 mm间距的QFP在40 mm边长的面积上只容纳304个 I/O )。

(2)封装可靠性高(不会损坏引脚),焊点缺陷率低,焊点牢固。

(3)管脚水平面同一性较QFP容易保证,因为焊锡球在溶化以后可以自动补偿芯片与PCB之间的平面误差。

(4)回流焊时,焊点之间的张力产生良好的自对中效果,允许有50%的贴片精度误差。

(5)有较好的电特性,由于引线短,导线的自感和导线间的互感很低,频率特性好。

(6)能与原有的SMT贴装工艺和设备兼容,原有的丝印机、贴片机和回流焊设备都可使用。

BGA的兴起和发展尽管解决了QFP面临的困难,但它仍然不能满足电子产品向更加小型、更多功能、更高可靠性对电路组件的要求,也不能满足硅集成技术发展对进一步提高封装效率和进一步接近芯片本征传输速率的要求,所以更新的封装CSP(Chip Size Package,芯片尺寸封装)又出现了,它的英文含义是封装尺寸与裸芯片相同或封装尺寸比裸芯片稍大。日本电子工业协会对CSP规定是芯片面积与封装尺寸面积之比大于80%。CSP与BGA结构基本一样,只是锡球直径和球中心距缩小了、更薄了,这样在相同封装尺寸时可有更多的 I/O 数,使组装密度进一步提高,可以说CSP是缩小了的BGA。图5展示的是行业领先内存厂商Kingmax生产的基于CSP封装技术的内存芯片。

CSP之所以受到极大关注,是由于它提供了比BGA更高的组装密度,而比采用倒装片的板极组装密度低。但是它的组装工艺却不像倒装片那么复杂,没有倒装片的裸芯片处理问题,基本上与SMT的组装工艺相一致,并且可以像SMT那样进行预测和返工。正是由于这些无法比拟的优点,才使CSP得以迅速发展并进入实用化阶段。目前日本有多家公司生产CSP,而且正越来越多地应用于移动电话、数码录像机、笔记本电脑等产品上。从CSP近几年的发展趋势来看,CSP将取代QFP成为高I/O引线IC封装的主流。

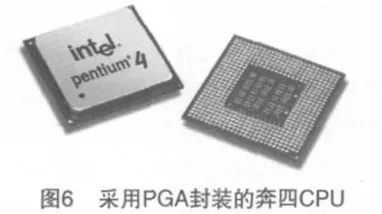

6 主流C PU 封装技术——PGA

PGA(Pin Gird Array Package,格栅阵列封装)是最常见的CPU封装方式之一,目前大多数CPU均采用此类封装方式,如图6。PGA封装最大的优点是安装方便,适用于高频率芯片。PGA封装在芯片下方围着多层方阵形的插针,每层方阵形插针是沿芯片的四周、间隔一定距离排列的,根据针脚数目的多少,可以围成2~6圈。PGA封装缺点是耗电量较大。

从486时代开始,出现了一种名为ZIF(Zero Insertion Force Socket,零插拔力插槽)的CPU插槽,使用PGA封装的CPU可以很轻松地插入这种插槽中,并将扳手压回原处,利用插槽本身的特殊结构产生的挤压力,使CPU的针脚与插槽“亲密”接触。反之,拆卸CPU时只须将插槽的扳手轻轻抬起,则压力解除,CPU即可轻松取出。这种插槽一直沿用至今,专门用于安装和拆卸PGA封装的CPU。

7 高性能芯片封装首选——LGA

LGA全称是Land Grid Array,直译就是栅格阵列封装。这种封装技术实际上是PGA 封装的改良。和PGA封装相比,LGA首先将底部的所有引脚去掉,转而变成了平面上的大量触点,如图7。这样一来就彻底消除了PGA封装引脚密度增加之后相互的信号干扰问题。LGA封装可以直接上锡装在PCB上,也可以通过LGA插座与芯片连接,在采用这样的连接方式后,芯片与PCB的距离得以显著缩短,使得LGA封装的电气性能更好于PGA。

正是因为LGA封装拥有更为优秀的特性,使得当今各种高密度的CPU、FPGA、DSP等芯片都纷纷转向LGA封装,其中Intel早在2005年就将旗下的Pentium、Celeron处理器转为LGA封装,从而保证CPU频率的提升不受封装电气性能的阻碍,其它芯片厂商也开始全面为用户提供LGA封装的产品。毫无疑问,LGA封装将会在未来逐步取代PGA,成为主流的芯片封装形式。

8 新兴力量—MCM

BGA封装比QFP先进,但它的芯片面积/封装面积的比值仍很低。这时有人设想,当单芯片一时还达不到多种芯片的集成度时,能否将多个集成电路芯片在高密度多层互联基板上用表面安装技术(SMT)组装成为多种多样电子组件、子系统或系统。由这种想法产生出多芯片组件MCM(Multi Chip Model)。它将对现代化的计算机、自动化、通讯业等领域产生重大影响。Intel推出的新一代处理器酷睿2双核处理器采用了MCM技术,拥有两个处理核心,能更好地运行多个程序,现在酷睿2四核处理器也已经开始大量上市,从这里开始,Intel CPU封装历史又要迈开新的一步。

MCM的特点有:

(1)封装延迟时间缩小,易于实现组件高速化;

(2)缩小整机/组件封装尺寸和重量,一般体积减小1/4,重量减轻1/3;

(3)可靠性大大提高;

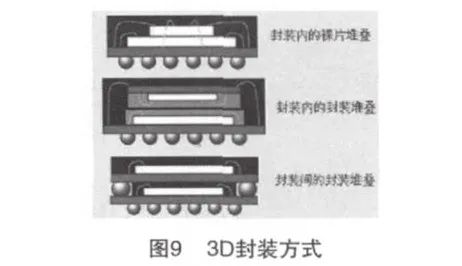

9 封装极致—3D 封装技术

在上述文章中我们介绍的所有封装技术,伴随着芯片体积的增加最后封装出来的产品面积也将会显著增加。那在现有技术条件和有限的空间内,如何进一步提升晶体管的密度?业界想到了让芯片纵向发展的办法。3D封装技术也因此诞生。3D封装可以通过两种方法实现:封装内的裸片堆叠和封装堆叠,如图8,封装堆叠又可分为封装内的封装堆叠和封装间的封装堆叠。两种方法各有利弊。总体上说:

(1)封装堆叠已经研发出不同的形式,这种封装使得能够堆叠来自不同供应商和混合集成电路技术的裸片,也允许在堆叠之前进行预烧和检测。

(2)封装堆叠包括翻转一个已经检测过的封装,并堆叠到一个基底封装上面,后续的互连采用线焊工艺。封装堆叠的装配过程类似于裸片堆叠CSP。封装堆叠在印制板装配的时候需要另外的表面安装堆叠工艺。

(3)因为裸片堆叠CSP在开发Z方向空间(即高度)的同时还保持了其X和Y方向上的元件大小(厚度即使增加也是非常小),这种封装已经被很多手机应用所接受。裸片堆叠CSP封装的主要缺点在于堆叠中的一层集成电路出现问题,所有堆叠的裸片都将报废,但毫无疑问裸片堆叠能够获得更为紧凑的芯片体积。

在裸片堆叠技术领域,业界最大的内存、闪存制造商三星对此有着极为深入的研究。早在2006年初,三星就宣布了独家用于内存芯片的3D封装技术。三星公司将这种新技术命名为“晶圆级的堆叠工艺”,简称WSP。现有的芯片封装依赖于对印刷电路板的有线连接,这种有线连接需要互连之间存在空间,以消除干扰,但是在制造高密度内存之时,这种空间会成为制约因素。三星宣布的“通过矽”的互相连接技术,本质上是激光在内存芯片之间打孔,然后以导体材料填充这些孔,以产生垂直互连效果。三星公司则在一个封装中堆叠了8个2 GB NAND芯片。这种容量16 GB的NAND芯片高度只有半个毫米(图9)。

由于各种裸片堆叠技术的逐步成熟,在未来许多3D封装都将会转向裸片堆叠以进一步降低体积。我们甚至可以期待在不久的将来通过3D封装技术,一张SD卡的容量可以轻松突破20GB!

10 结语

究竟一片简单的芯片凝结了多少智慧我们无从考究,但要让一片芯片正常运行往往需要成千上万种技术的良好配合以及正常工作。作为芯片制造中不可或缺的封装技术,每次封装的进化都将会带动整个芯片制造行业的巨大发展。芯片封装就像是半导体行业的风向标,从一部封装技术的简史中,我们就得以窥探半导体技术的发展足迹。

扫二维码用手机看

关联新闻

麦斯克电子四支部组织开展学雷锋活动

深化奖与惩 促进改与升 麦斯克电子一支部召开党员大会